1.1 逻辑门简介

在本教程中,我们将对逻辑门进行简要介绍。我们将了解TTL电路和CMOS电路中的不同逻辑电平,以及一些简单的逻辑门,如OR、NOT、NAND、AND等。

逻��辑门简介

逻辑门是数字电子学的核心。逻辑门是一种电子设备,用于对二值信号进行函数运算。逻辑门是数字电路的基本构建模块。

一般来说,所有逻辑门都有一个输出和两个输入。某些逻辑门,如NOT门或反相器,只有一个输入和一个输出。逻辑门的输入被设计为仅接收二进制数据(仅低电平0或高电平1),通过接收电压输入实现。

低逻辑电平表示0伏,高逻辑电平表示3伏或5伏正电源电压。

我们可以通过连接任意数量的逻辑门来设计所需的数字电路。在实际应用中,我们通过将大量逻辑门集成在集成电路(IC)中,从而节省大量逻辑门所占用的物理空间。通过使用集成电路(IC),我们还可以以高速度执行复杂操作。

通过组合逻辑门,我们可以设计许多特定的电路,如触发器、锁存器、多路复用器、移位寄存器等。

数字逻辑电平

逻辑电平被定义为信号的特定状态或电压。我们知道,0和1是逻辑门的两个状态。逻辑电平0和1分别被称为低电平(LOW)和高电平(HIGH)。在数字电子学中,这些二进制逻辑电平在数据存储和数据传输中起着至关重要的作用。

一般来说,这些逻辑电平可以被理解为开(ON)和关(OFF)状态。如前所述,逻辑电平是通过电源电压引入到逻辑门的。如果逻辑门的电源电压为0伏,则表示低逻辑电平或关(OFF)状态。

同样,如果逻辑门的电源电压为5伏或3.3伏(对于现代集成电路),则表示高逻辑电平�或开(ON)状态。制造商在设计集成电路时,通常遵循TTL(晶体管 - 晶体管逻辑)作为标准电压电平。

什么是高电平有效和低电平有效?

我们在集成电路和微控制器中看到高电平有效输入和低电平有效输入引脚。你知道它们的真正含义吗?它们只是描述引脚是如何被激活的。

这意味着低电平有效的引脚必须连接到低逻辑电平或地(GND)。同样,高电平有效的引脚必须连接到高逻辑电平,即3.3伏或5伏。

让我们以一种简单的方式理解这一点。当我们看到移位寄存器集成电路中的使能引脚CE,如果没有在其上方画一条横线,我们就将其连接到低电平输入,即接地0伏。相反,如果使能引脚上方有一条横线(),我们就将其连接到高电平输入,即3.3伏或5伏电源,以启用该引脚。

TTL逻辑电平

TTL逻辑电平是大多数逻辑设备的标准逻辑电平。TTL代表晶体管 - 晶体管逻辑。晶体管是受电控制的开关。逻辑家族的电压电平为:

- (高电平输出电压的最小值)

- (低电平输出电压的最大值)

- (设备识别为高电平信号的最小输入电压)

- (设备识别为低电平信号的最大输入电压)

如果观察TTL逻辑电平,我们可以看到高电平输出的最小电压为2.7伏。这意味着,当设备输出高电平时,电压至少应为2.7伏。

同样,高电平输入的最小电压为2伏。因此,大于2伏的电压将被TTL设备视为逻辑1。0.8伏到2伏之间的电压被称为噪声容限。

同样,低电平输出的最大电压为0.4伏。这意味着,当设备输出低电平时,电压应小于0.4伏。同样,低电平输入的最大电压为0.8伏。

因此,小于0伏的电压将被TTL设备视为逻辑0。因此,当逻辑设备被施加0.8伏到2伏之间的电压时,设备的逻辑电平将在高电平和低电平之间变化。这种情况被称为“浮动”。

TTL设备的输入和输出容差的另一种程序为:

CMOS逻辑电平

CMOS逻辑设备也被称为3.3伏设备,因为CMOS设备的最大电压电平为3.3伏。这是一种先进技术,可以在低电源(3.3伏而不是5伏)下运行设备。

大多数情况下,我们使用5伏设备(TTL兼容)来设计逻辑门,因此这些CMOS设备被用于与TTL设备接口。CMOS设备可以与任何TTL设备接口,且不需要任何额外组件。

例如,CMOS设备的高逻辑电平(1)的最小值为2.4伏。因此,该设备可以与TTL设备接口,TTL设备的高逻辑电平()的最小输入电压为2伏。

但是,在将TTL设备与CMOS设备(3.3伏和5伏)接口之前,我们需要检查3.3伏设备是否为5伏容错。因为许多设备在施加超过3.6伏的电压时会永久损坏芯片。我们可以使用分压电路或电平转换器来控制5伏电压信号。

噪声容限

逻辑电平的噪声容限被定义为逻辑门的高输入电平的最大低电压( max)和低输入电平的最大电压( min)之间的电压差。噪声容限也被定义为电压信号超出精确高电平或精确低电平阈值的量。

让我们通过一个例子来清楚地理解这一点。当一个逻辑电路在0伏和1.2伏之间切换时,任何低于0.2伏的电压都被视为低电平(0)。任何高于1伏的电压都被视为高电平(1)。

CMOS逻辑设备的噪声容限或噪声裕度比TTL逻辑设备更高,因为它们的高逻辑电平( min)的最小输出电压更接近电源电压,而低逻辑电平( max)的最大输出电压接近0。因此,噪声容限是逻辑电路能够承受的最大噪声量。

如果我们施加一定量的噪声电平,我们无法确定电路是否会响应。噪声电平是由外部干扰(如电源电压波动和其他导体中的噪声)引起的不想要的电压电平。

电路能够承受的噪声电平被称为“噪声免疫性”或“噪声容限”。对于TTL设备,输出电压的容差范围高于输入电压的容差范围。

简单的二极管逻辑门

二极管可以像开关一样工作,因此它们被用于数字逻辑运算和开关。对于低阻抗和高阻抗状态,二极管分�别工作在正向偏置和反向偏置状态。

二极管仅在一个方向(正向偏置)导电,而在反向偏置条件下保持关闭状态。因此,它表现得像一个开关。现在,让我们看看一些由二极管和电阻构成的简单二极管逻辑门。

OR门

由两个二极管设计的简单OR门如图所示。两个二极管为该电路提供输入。在此电路中,逻辑高电平(1)由+5伏表示,逻辑低电平(0)由0伏或地表示。

在下图中,两个输入端未连接,因此输出为0,即低电平。

如果两个输入中的任何一个连接到+5伏,则二极管正向偏置并导电。因此,输出为逻辑高电平,即1。

如果两个输入(两个二极管)都连接到+5伏的电压,则两个二极管都处于正向偏置状态,这使得OR电路的输出设置为高电平。

OR门的功能在数学上表示为 ,其中 是OR门的输出, 和 是输入。逻辑OR门的真值表、逻辑符号和电路图如下所示。

AND门

由两个二极管设计的简单AND门如图所示。在此电路中,驱动电压 通过电阻 连接到两个并联的二极管。两个二极管为该电路提供输入。

在此电路中,逻辑高电平(1)由+5伏表示,逻辑低电平(0)由0伏或地表示。

在下图中,两个输入端未连接,因此输出也为0,即低电平。

如果两个输入中的任何一个连接到+0伏,则二极管反向偏置,不会导电,并使输出保持低电平,即0。

如果两个输入(两个二极管)都连接到+5伏的电压,则两个二极管都处于正向偏置状态,这使得AND电路的输出设置为高电平。

AND门的功能在数学上表示为 ,其中 是AND门的输出, 和 是输入。逻辑AND门的真值表、逻辑符号和电路图如下所示。

晶体管逻辑门

与二极管类似,晶体管也充当电子开关。我们也可以使用晶体管设计逻辑门。让我们了解一下由晶体管构成的逻辑门。

NOT门

NOT门通常被称为反相器。它产生与输入完全相反的输出。它只有一个输入和一个输出。NOT门的输出始终是其输入的反相。当低电平信号(0伏)连接到NOT门的输入时,输出将是高电平(逻辑1)。

同样,如果高电平信号(+5伏)连接到输入,则输出将是低电平(逻辑0)。NOT操作用“-”横线符号表示。如果NOT门的输入是 ,输出是 ,则NOT门的操作表示为 ,读作“X非”。

由晶体管设计的NOT门如下图所示。输入信号通过一个电阻连接到晶体管的基极。该晶体管电路由+5伏电源供电。

当输入连接到低电平信号(0伏)时,晶体管将处于反向偏置状态。因此,没有电流会流过晶体管,它保持在关闭状态。由于没有电流流过晶体管,电阻上也不会有电压降。因此,输出将对应于+5伏,使输出逻辑为高电平。

但如果输入连接到+5伏,则输出电压将变为0伏。由晶体管设计的NOT门如下图所示。

除了NOT门,还可以使用晶体管设计另外两个门:NAND门和NOR门。这些门被称为“通用门”。

NAND门

NAND门能够执行三种操作:AND、OR和NOT。这个门是NOT门和AND门的组合。NAND门的输出等于AND门的反相。

NAND门有两个输入 和 ,以及一个输出 。输入通过二极管连接到晶体管。NAND门电路由+5伏供电。

当两个输入都连接到5伏的电源时,二极管 和 都处于关闭状态。然后晶体管 可以通过电阻从电源电压导通。因此,晶体管处于导通状态,输出电压 (饱和)变为0。

同样,当输入端施加低电平电压,即0伏时,晶体管将关闭,输出电压变为+5伏。NAND门在数学上表示为 。

因此,��只有当两个输入都为高电平时,NAND门的输出才为低电平。对于任何其他输入组合,输出都为高电平。NAND门的真值表、逻辑符号和晶体管电路图如下所示。

NOR门

NOR门是NOT门和OR门的组合。NOR门的输出等于OR门的反相。NOR门有两个输入 和 ,以及一个输出 。

设计的NOR门电路中有两个NPN晶体管,电源电压为+5伏。

当NOR门的两个输入都连接到0伏时,晶体管 和 处于关闭状态。因此,没有电流通过电阻,电阻两端没有电压降。此时,输出电压等于电源电压+5伏,即高电平逻辑状态。

如果任何一个输入连接到+5伏,晶体管将处于导通状态。因此,电压降会很大。因此,电路的输出电压将为0伏,即等于地电压。

NOR门在数学上表示为 。

因此,只有当两个输入都为低电平时,NAND门的输出才为高电平。对于任何其他输入组合,输出都为低电平。NOR门的真值表、逻辑符号和晶体管电路图如下所示。

74系列逻辑集成电路

7400系列集成电路于20世纪60年代初推出。尽管还有许多其他用于逻辑门的集成电路,但7400 TTL系列集成电路因其简单的编号方案和标准而成为最受欢迎的。以下是一些规格和主要特点。

74系列集成电路采用双极型晶体管技术制造,因此被称为TTL系列集成电路。(TTL代表晶体管 - 晶体管逻辑)。7400系列集成电路的工作电源为+5伏,这一电压电平成为逻辑电路的标准,直到CMOS技术的发展。

这些是用于逻辑电路设计的广泛使用的集成电路系列。在7400系列集成电路之前,我们有TTL系列芯片。摩托罗拉公司推出了一种名为MTTL的逻辑家族,即摩托罗拉晶体管 - 晶体管逻辑。

其他研究人员和制造商,如Signetics、Fairchild和National Semiconductor,也推出了一些其他系列的集成电路。

有几种集成电路家族编号为74xx00。其中的“xx”表示集成电路的类型和规格。不同类型的集成电路系列包括74LS00、74HC00和74HCT00等。让我们来看一下每个集成电路系列的规格和用途。

- 74LS系列:这是使用TTL电路的低功耗肖特基家族。这些集成电路操作速度快,但比其他逻辑家族消耗的功率更多。

- 74HC系列:这是一个高速CMOS家族。这些集成电路结合了4000系列的低功耗特性和74LS系列的速度。

- 74HCT系列:这是74HC家族的一个非常特殊的版本。它具有与74LS系列兼容的TTL输入。因此,它可以轻松地与74LS系列接口。74HCT家族被用作74LS系列的替代品,因为它们的功耗要求较低。

74HCT系列的缺点是它们对噪声的免疫力较低,即它们的噪声容限较小。

由于CMOS电路的静电敏感性,74HC系列和74HCT系列使用了CMOS电路。这意味着如果在集成电路充电时触摸其任何引脚,可能会损坏集成电路。

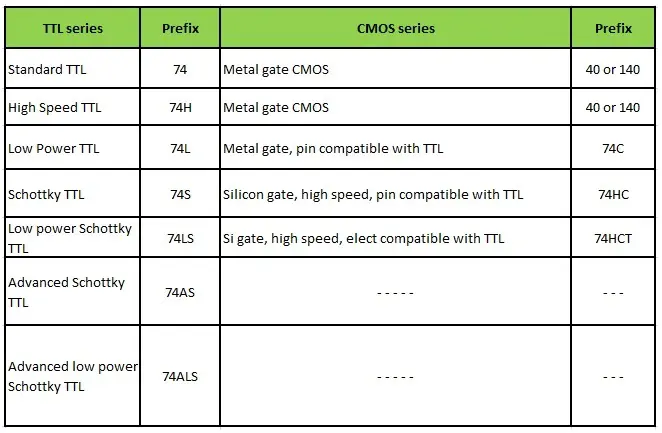

TTL和CMOS系列集成电路的前缀如下表所示。

以下是一些用于逻辑门设计的常用集成电路:

四输入双门逻辑门

- 74LS00:四输入双门NAND门

- 74LS01:四输入双门NAND门,开路输出

- 74LS02:四输入双门NOR门

- 74LS03:四输入双门NAND门,开路输出

- 74LS08:四输入双门AND门

- 74LS09:四输入双门AND门,开路输出

- 74LS32:四输入双门OR门

- 74LS132:四输入双门NAND门,施密特触发输入

- 74LS37、74LS32、74LS28:四输入双门NOR门

- 74LS26:四输入双门NAND门,开路输出(15V)

- 74LS28:四输入双门NAND门,开路输出(15V)

- 74LS33:四输入双门NOR门,开路输出

- 74LS38:四输入双门NOR门,开路输出

- 74LS38:四输入双门NAND门,开路输出

三输入三门逻辑门

- 74LS10:三输入三门NAND门

- 74LS11:三输入三门AND门

- 74LS12:三输入三门NAND门,开路输出

- 74LS27:三输入三门NOR门

- 74LS15:三输入三门AND门,开路输出

双输入四门逻辑门

- 74LS13:双输入四门NAND门,施密特触发

- 74LS20:双输入四门NAND门

- 74LS21:双输入四门AND门,开路输出

- 74LS22:双输入四门NAND门,开路输出

- 74LS40:双输入四门NAND门

- 74LS30:八输入NAND门

六输入反相器

- 74LS04:六输入反相器

- 74LS05:六输入反相器,开路输出

- 74LS14:六输入反相器,施密特触发输入

- 74LS19:NAND门,施密特触发,图腾柱输出

- 74LS23:2个四输入NOR门,带选通信号

- 74LS25:2个四输入NOR门,带选通信号

- 74LS30:八输入NAND门

- 74LS39:4个双输入NAND门,开路输出